Product Summary

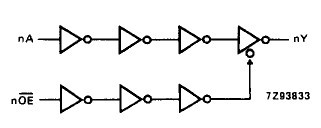

The 74hct125n is a high-speed Si-gate CMOS device and is pin compatible with low power Schottky TTL(LSTTL). The 74hct125n is specified in compliance with JEDEC standard no. 7A. The 74hct125n has four non-inverting buffer/line drivers with 3-state outputs. The 3-state outputs (nY) are controlled by the output enable input (nOE).

Parametrics

74hct125n absolute maximum ratings: (1)tPHL/ tPLH propagation delay nA to nY: +25℃: typ=15ns, 25ns; -40 to +85℃: 31ns; -40 to +125℃: 38ns; (2)tPZH/ tPZL 3-state output enable time nOE to nY: +25℃: typ=15ns, 28ns; -40 to +85℃: 35ns; -40 to +125℃: 42ns; (3)tPHZ/ tPLZ 3-state output disable time nOE to nY: +25℃: typ=15ns, 25ns; -40 to +85℃: 31ns; -40 to +125℃: 38ns; (4)tTHL/ tTLH output transition time: +25℃: typ=5ns, 12ns; -40 to +85℃: 15ns; -40 to +125℃: 18ns.

Features

74hct125n features: (1)Output capability: bus driver; (2)ICC category: MSI.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

74HCT125N |

NXP Semiconductors |

Buffers & Line Drivers QUAD 3-STATE BUS BUF |

Data Sheet |

Negotiable |

|

||||||||||||

|

74HCT125N,652 |

NXP Semiconductors |

Buffers & Line Drivers QUAD 3-STATE BUS BUF |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))